Research

AION Lab focuses on analog/mixed-signal ICs, neural interface system ICs, physical AI sensor ICs, and process-in-memory.

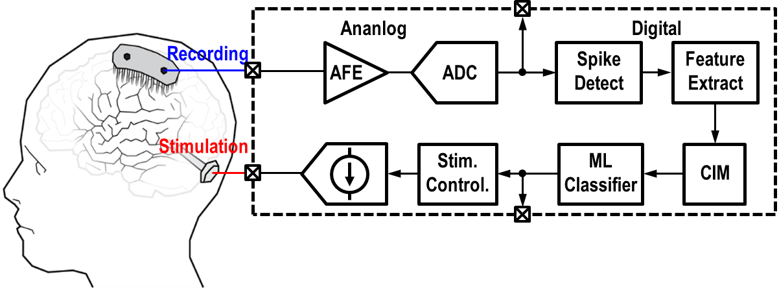

1) Neural Interface System IC

- High-density multi-channel neural recording ICs for next-generation neurotechnology

- Artifact-tolerant, wide-dynamic-range front-ends for closed-loop interfaces

- Recording/stimulation/closed-loop circuit architectures

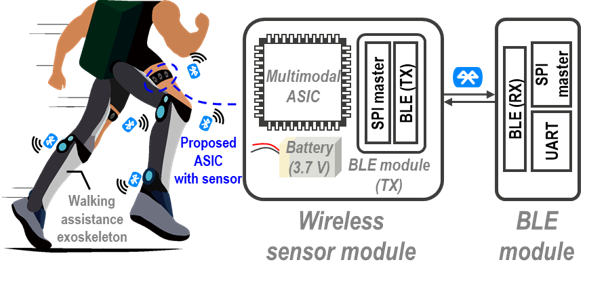

2) Sensor Interface ICs for Physical AI

- Multimodal wireless biosignal sensor interfaces for wearable robotics

- Ultra-low-power sensing SoCs and interference-tolerant acquisition circuits

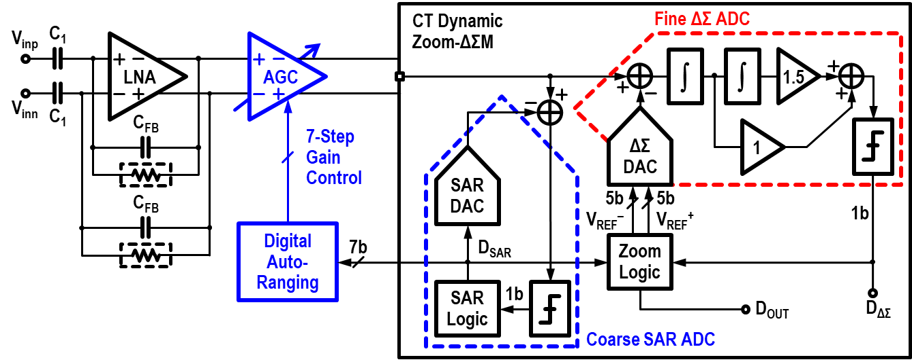

3) Data Converters for Bio/Sensor Readout

- ΔΣ ADC (CT/DT hybrid), NS-SAR, time-based readout architectures

- Dynamic-range enhancement and noise-shaping techniques for robust acquisition

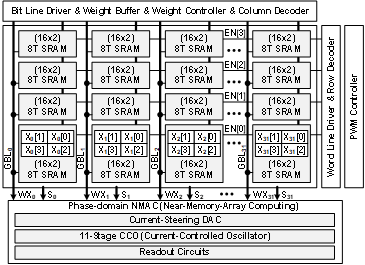

4) Process-in-Memory / Compute-in-Memory

- Energy-efficient mixed-signal PIM/CIM direction for edge intelligence

- Co-design of sensing + on-chip intelligence under non-idealities

Selected Projects

- imec (2024–2026): High-density multi-channel neural recording IC (SAR ADC, reference buffer, LDO)

- NRF (2020–2024): Multimodal wireless sensor interface circuits and flexible biosignal sensors (Project lead)

- Samsung LSI (2018–2023): Sub-aF capacitive sensor interface for E-Nose + drift compensation techniques